- D-Matrix從AI培訓轉變為推理硬件創新

- 海盜使用LPDDR5和SRAM來減少HBM依賴

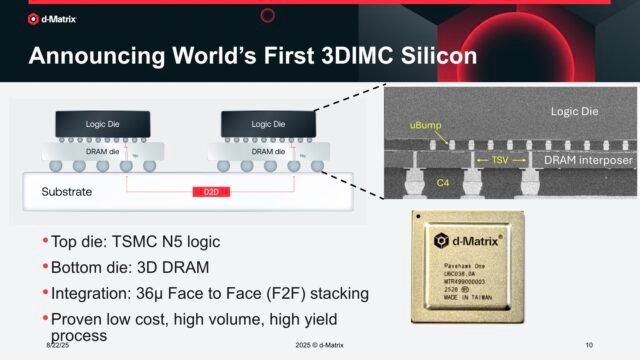

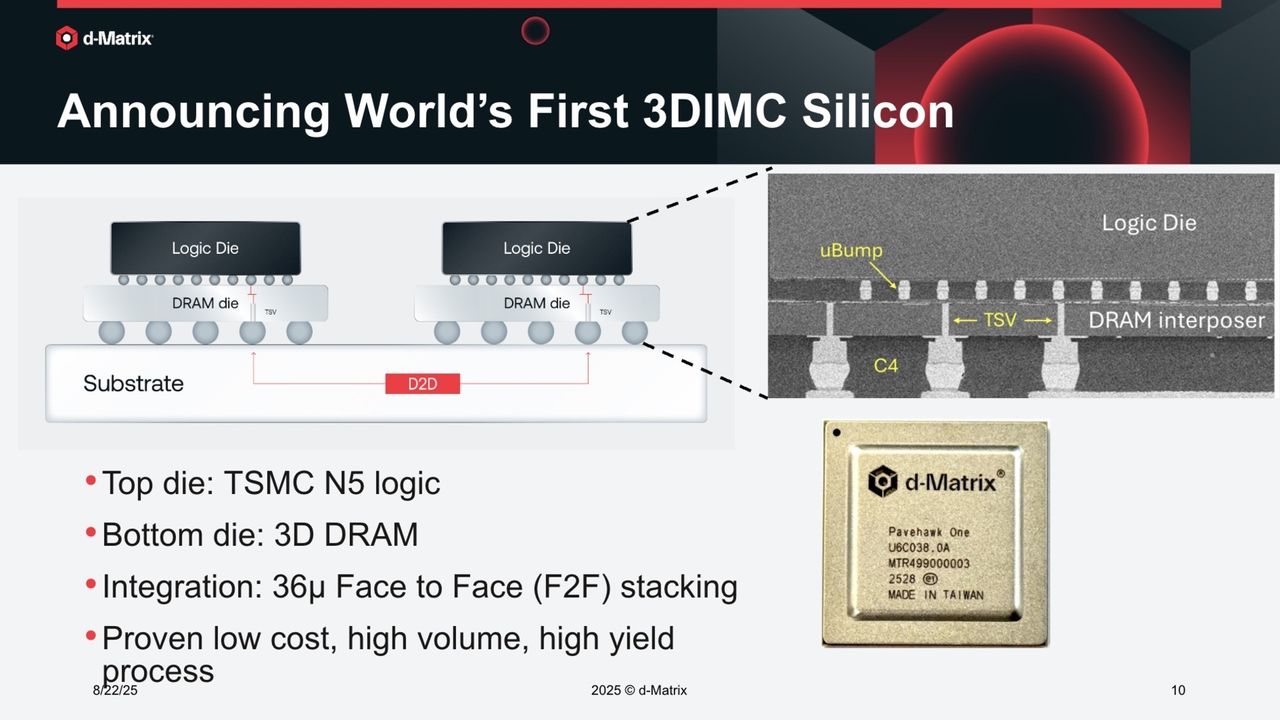

- Pavehawk結合了堆疊的DRAM和邏輯,以減少潛伏期

Sandisk和SK Hynix最近簽署了一項協議,以開發“高帶寬閃光燈”,這是一種基於NAND的HBM替代品,旨在將更大的非揮發容量帶入AI加速器。

D-Matrix現在將自己定位為挑戰者在競賽中加速人工智能工作量的挑戰者。

儘管大部分行業都專注於使用HBM的培訓模型,但該公司選擇專注於AI推斷。

記憶牆的另一種方法

它當前的設計D-Matrix Corsair使用了基於chiplet的架構,其LPDDR5和2GB的SRAM使用。

這個想法不是追逐更昂貴的內存技術,而是共同包裝加速發動機和 DRAM,在計算和內存之間建立一個更緊密的鏈接。

這項稱為D-Matrix Pavehawk的技術將與3DIMC一起啟動,該技術有望與HBM4競爭AI推斷,以使用10倍帶寬和每個堆棧的能源效率。

該平台建立在TSMC N5邏輯模具上,並與3D堆疊的DRAM結合使用,旨在使計算和內存比傳統的佈局更接近。

通過消除一些數據傳輸瓶頸,D-Matrix表明它可以減少延遲和功率使用。

鑑於其技術路徑,D-Matrix似乎致力於將多個DRAM模化在邏輯矽上方,以進一步推動帶寬和容量。

該公司認為,這種堆疊的方法可能會在績效增長中提供數量級,同時使用較少的能量進行數據移動。

對於努力縮放記憶界面的限制的行業,該提案是雄心勃勃的,但仍未得到證實。

值得注意的是,圍繞推理加速器的內存創新並不是什麼新鮮事。

其他公司一直在嘗試緊密耦合的內存和計算解決方案,包括具有內置控制器的設計或通過CXL等互連標準的鏈接。

但是,D-Matrix試圖通過集成自定義矽來改進成本,權力和性能之間的平衡。

這些發展的背景是HBM周圍的持續成本和供應挑戰。

NVIDIA等大型玩家可以保護頂級HBM零件,但是小型公司或數據中心通常必須為低速模塊而定。

這種差異創造了一個不平坦的競爭環境,其中最快的記憶直接構成了競爭力。

如果D-Matrix確實可以以低成本和較高容量的替代方案進行交付,則它將解決數據中心級別縮放推斷的中心疼痛點之一。

儘管有“ 10倍更好的性能”和“ 10倍更好的能源效率”的說法,但D-Matrix仍處於其描述為多年旅程的開始。

許多公司試圖解決所謂的記憶牆,但在實踐中很少有人重塑市場。

AI工具的興起和對每個LLM的依賴都表明了可擴展推理硬件的重要性。

但是,無論是Pavehawk和Corsair是否會成熟地採用廣泛採用的替代方案或保持實驗性尚待觀察。

通過 服務房屋

您可能還喜歡

#DMatrix想要用芯片堆疊的DRAM和激進的3DIMC加速器設計將HBM定價粉碎