- Pezy堅持要求工作負載的需求比Lockstep主流執行允許的獨立性更多

- PEZY SC4S模擬聲稱比上一代設計大大提高了效率

- 在TSMC 5nm上製造的芯片,尺寸異常大的芯片

在一家以非常規硬件而聞名的日本小型公司的Hot Chips 2025上,介紹了其最新項目PEZY SC4S。

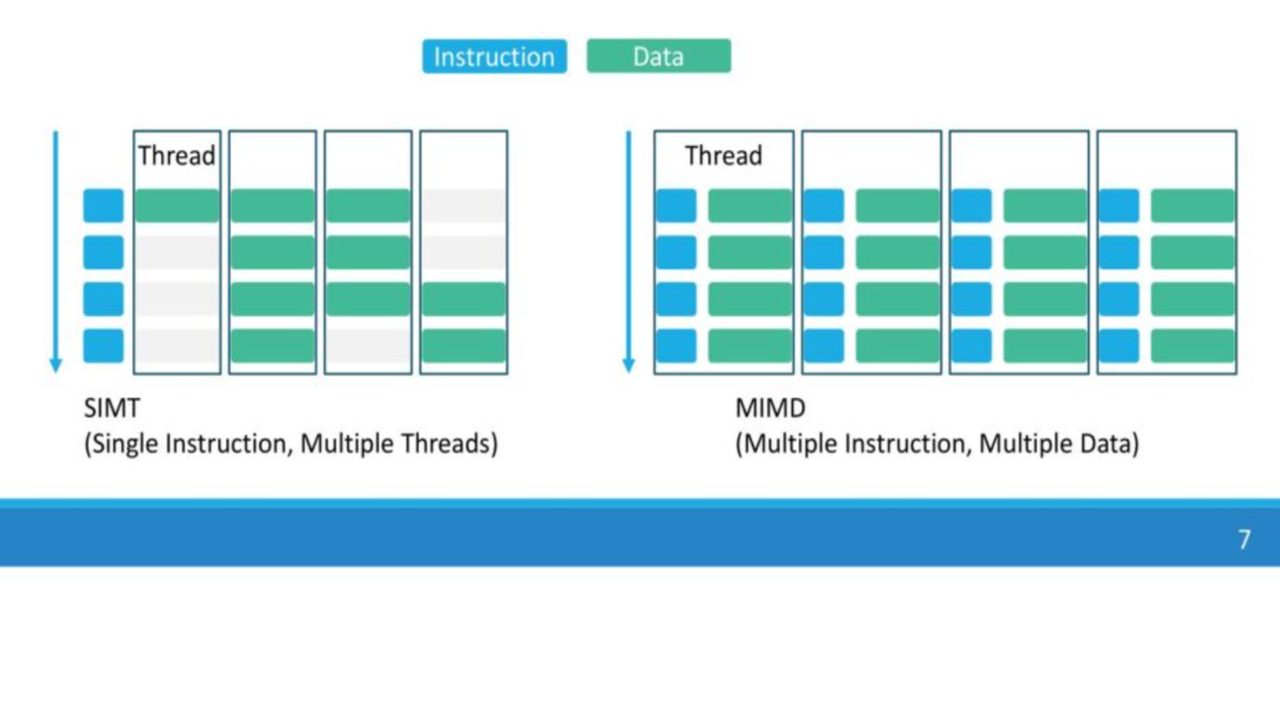

與已圍繞單個指令進行標準化的主流芯片製造商不同,PEZY Computing繼續追求多個指令多個數據(MIMD)。

MIMD可以比喻為一個國家,城市,城市和村莊的社會,每個單位都具有一定程度的獨立性,而不是遵循一個中央權威。

建築和製造選擇

MIMD不是一個新主意 – 畢竟,每個現代 用於編程的筆記本電腦一次執行多個任務,但很少在涉及數百或數千個核心的真正規模上實施。

設計理念假設未來的工作負載並不總是從鎖定執行中受益,並且更獨立的線程處理可能會成為必不可少的。

這使其策略與占主導地位的全球市場的最佳最佳CPU競爭者的方向不同。

SC4S是在TSMC的5NM工藝上製造的,就物理足跡而言,SC4S並不是很小的芯片。

它的大小約為556mm2,它比許多消費者或工作站處理器大得多。

但是,重點不是最小化矽區域,而是測試大規模並行性的好處是否超過成本。

CPU擁有數百個核心的想法已經存在了一段時間。佩茲認為,在集中式方法掙扎的情況下,許多小型的半自治核心可能會成功。

實際上,該公司押注某些專業領域的計算需求可以證明這一規模是合理的,儘管這種方法對於更廣泛的消費者採用可能是不切實際的。

但是,Pezy Computing發布的是性能模擬,而不是最終的矽基準,這自然會提出有關這些主張在實踐中的表現如何的疑問。

與較早的SC3設計相比,SC4S預計將在處理DGEMM工作負載時提供的功率效率超過兩倍。

同時,基因組序列比對中使用的史密斯 – 水手算法的模擬表明性能增加了幾乎四倍。

儘管這些數字在紙上令人印象深刻,但在獨立測試驗證它們之前,懷疑仍然存在。

從歷史上看,半導體開發中的大膽預測並不總是與一旦真正的硬件船的測量結果保持一致。

儘管SC4仍在開發中,但該公司已經將注意力轉移到了繼任者身上。

第五代處理器正在進行工作,暫定稱為PEZY 5,預計將使用3nm或更小的過程。

儘管技術或經濟挑戰構成了芯片開發中的這種長期時間表,但已設定了一個釋放窗口。

鑑於企業的規模,行業觀察者對時間表是否現實保持謹慎。

通過 服務房屋

您可能還喜歡

#日本小型芯片製造商敢於與怪物處理器打破技術規則